|

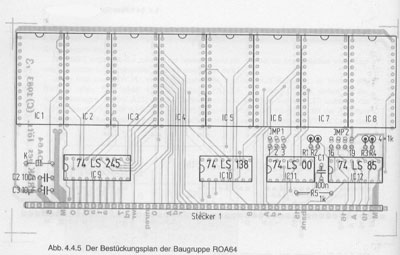

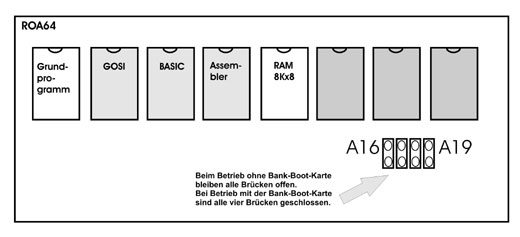

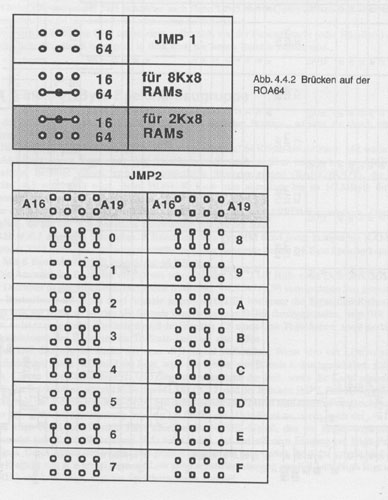

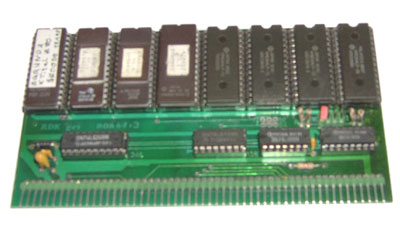

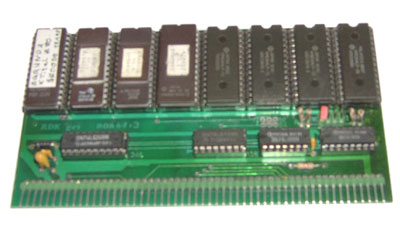

Da die beiden Vollausbau-CPUs keinen eigenen Speicher besitzen, müssen sie durch einen externen Speicher erweitert werden. Die Baugruppe ROA64 ermöglicht es, den Speicher auf 64KByte auszubauen. Mit weiteren ROA64-Baugruppen kann man den Speicherbereich noch darüber hinaus bis zu l MByte erweitern, benötigt jedoch noch eine zusätzliche Steuerbaugruppe (BANK/BOOT), die im Kapitel 4.5 vorgestellt wird. Beim HD64180 kann man allerdings bis zu 1/2 MByte direkt ansteuern, mit dem Z80 nur 64KByte. In die Baugruppe ROA64 kann man sowohl RAMs als auch EPROMs einstecken. Das ist möglich, da die 8K X 8-Bausteine miteinander kompatibel sind. Abb. 4.4.l zeigt den Schaltplan. 8 Bausteine vom Typ HM 6264 (oder kompatible RAMs), und/oder 2764 EPROMs sind vorgesehen. Jeder dieser Bausteine besitzt 8 KByte Speicherkapazität. Mit 8 Bausteinen erhält man damit 64 KByte. Die Auswahl der Bausteine erfolgt wie schon bei der SBC2 mit Hilfe eines Dekoders (IC10). Der Datenbus ist durch den bidirektionalen Bustreiber 74LS245 (IC9) vom internen Bus getrennt. Der Bustreiber wird durch zwei Signale angesteuert. DIR bestimmt die Signalfluß-Richtung. Liegt DIR auf High, so werden alle Signale vom A-Teil zum B-Teil durchgeschaltet, liegt DIR auf Low, so ist es umgekehrt. Zusätzlich muß der Eingang -CS einen Low-Pegel haben, sonst sind alle Datenleitungen des Bausteins im Tri-State-Zustand, also offen. Der DIR-Eingang ist direkt mit dem -RD-Signal verbunden. Wenn also ein Lesevorgang stattfindet und somit -RD auf Low liegt, wird der Treiber von B nach A durchgeschaltet, sofern auch -CS ein Low-Signal besitzt. Und dies ist immer dann der Fall, wenn die Karte adressiert wird. Die Selektion erfolgt mit Hilfe des 74LS85 (IC 12) und der Brücken JMP2. Das IC vergleicht die Signale der A-Seite mit der B-Seite. Mit den Brücken JMP2 stellt man einen zu vergleichenden Wert ein. Bei Übereinstimmung liegt am „= OUT" ein High-Pegel an, wenn auch der „= IN" einen High-Pegel hat. Dorthin führt aber das BANKSEL-Signal, das wir bisher noch nicht verwendet haben. Ein Widerstand (R5) sorgt dafür, daß bei offenem Eingang ein High-Pegel vorliegt. Der Ausgang des Vergleiches gelangt dann an ein paar Gatter, die dafür sorgen, daß der -CS-Eingang von IC9 genau dann auf Low geht, wenn der Ausgang von IC12 auf High liegt und -MREQ auf Low liegt, also ein Speicherwunsch vorliegt. Die Brücken JMP1 geben einem die Möglichkeit auch 2K X 8 Speicher zu verwenden, doch das ist nicht der Normalfall. Abb. 4.4.2 zeigt verschiedene Kombinationsmöglichkeiten für die Brückeneinstellung. Mit JMP2 stellt man die Adresse der Speicherkarte ein, bei der sie angesprochen wird. Eine eingezeichnete Linie entspricht einer eingesteckten Brücke. Wenn man die Z80-CPU verwendet und keine BANK/BOOT-Karte hat, so bleiben alle Brücken offen. Man erhält dann die Adresse FXXXX. Die Werte XXXX stehen für die Adreßleistungen AO bis A15, die durch den Prozessor bestimmt werden. „F" steht für die Adreßleitungen A16 bis A19. Die Z80-Vollausbau-CPU hat keine Ausgänge für die Adressen A16 bis A19. Daher sind sie auf dem Bus offen. Offene Leitungen haben bei TTL-ICs aber den Wert l, daher ergibt sich binär 1111 für AI6 bis A19, oder F in sedezimaler Schreibweise. Die Karte wird also von FOOOO bis FFFFF angesprochen. Arbeitet man mit der BANK/BOOT-Karte, so kann man auch andere Kombinationen verwenden. Soll die ROA64 zum Beispiel im Bereich AOOOO bis AFFFF angesprochen werden, so finden Sie in Abb. 4.4.2 unter „A" die entsprechende Brückenbelegung für den JMP2, für den Bereich 20000 bis 2FFFF nehmen Sie die Kombination bei „2". Abb.4.4.3 zeigt die Lötseite der Leiterplatte ROA64 und undAbb. 4.4.4 die Bestückungsseite. Abb. 4.4.5 zeigt den Bestückungsplan der Baugruppe. |